数字逻辑1-3章 复习笔记

数字逻辑1-3章复习笔记

第一章 开关理论基础

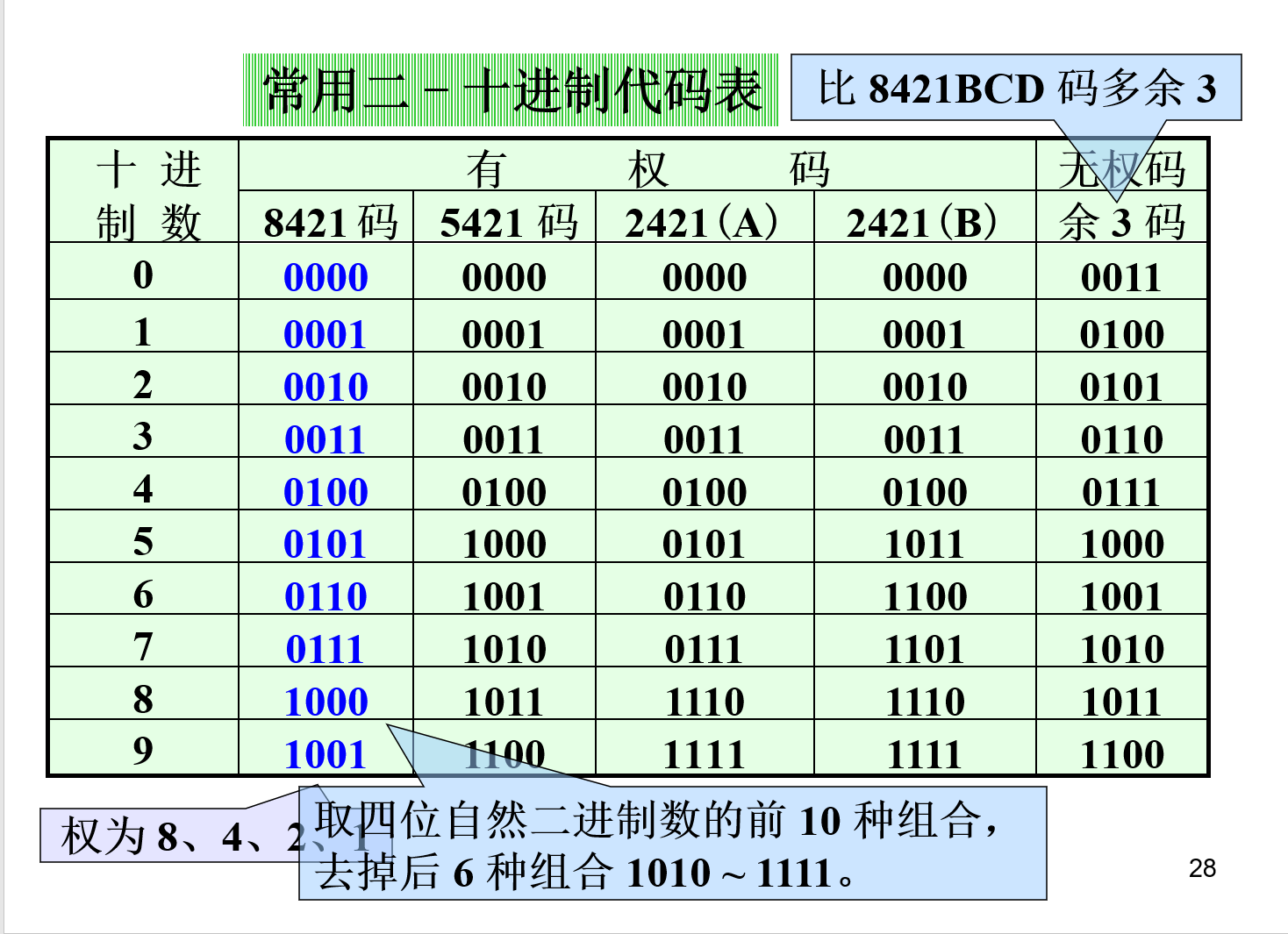

8421BCD

注意:8421bcd与一般数位不同,是逐字代换而不是整体进行计算!

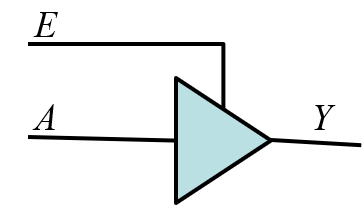

三态门

| E | A | Y |

|---|---|---|

| 0 | x | 高阻态 |

| 1 | 1 | 1 |

| 1 | 0 | 0 |

基本定律

交换律 A + B = B + A A · B = B · A

结合律 (A + B) + C = A + (B + C) (A · B) · C = A · (B · C)

分配律 A (B + C) = AB + AC

重点是这一条:A+BC=(A+B)(A+C)

吸收律

德摩根律/反演规则

对一个逻辑表达式Y,将“·”换为“+”,“+”换为“·”,1换为0,0换为1,将变量换为对应的非变量,非变量换为对应的变量,得反演式

- 变量的改变只对单变量有效,对长非号不能操作,需要保留

- 利用反演规则,可以求出一个函数的非函数

**变换时注意: ** (1) 不能改变原来的运算顺序:先与后或

对偶规则

对一个逻辑表达式Y,将“·”换为“+”,“+”换为“·”,1换为0,0换为1,得对偶式

对偶规则:两个函数式相等,则它们的对偶式也相等

变换时注意:(1) 变量不改变

(2) 不能改变原来的运算顺序:先与后或

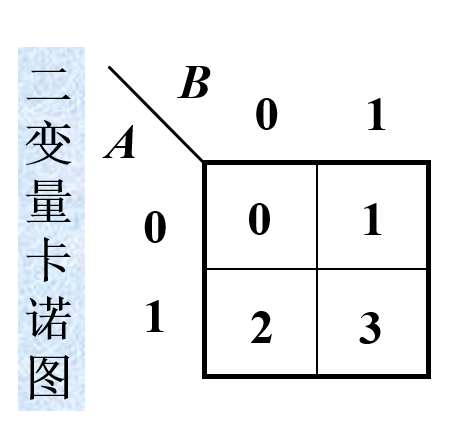

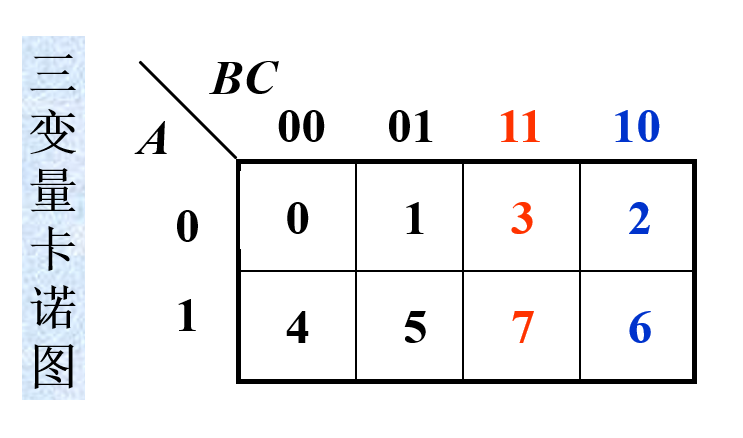

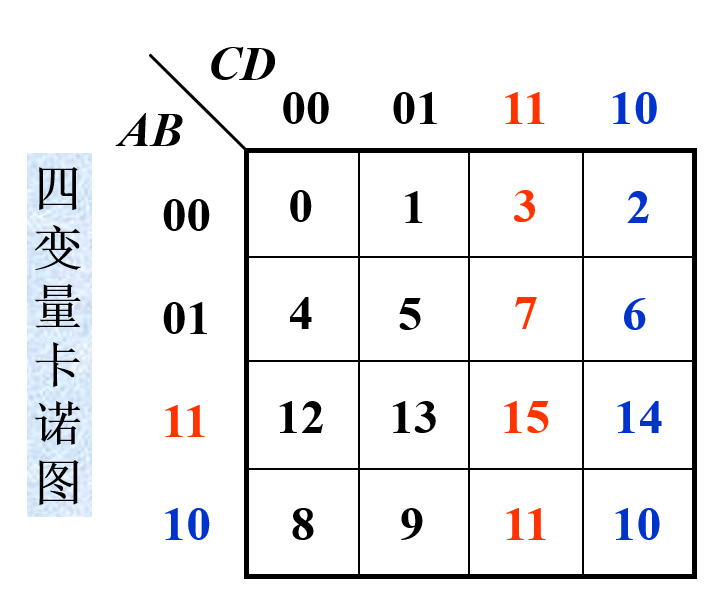

卡诺图

最小项

一个函数有n个变量,就有个最小项-

-

每项都有n个因子,每个变量都是其中的一个因子

-

因子可以是原变量,也可以是非变量

-

每一个逻辑函数都可以化成最小项表达式

-

两个最小项中只有一个变量互为反变量,其余变量均相同,称为相邻最小项,简称相邻项,两个相邻最小项相加可合并为一项,消去互反变量,化简为相同变量相与

如:

注意要以循环码排列以保证相邻性

-

画圈应先画大的,再画小的

-

每一个圈中至少要有一个格子是没有被其他圈所圈到的

-

无关项有约束项和随意项两种情况,其取值对逻辑函数值没有影响。因此,化简时应视需要将无关项方格看作 1 或 0,使包围圈最少而且最大,从而使结果最简。

-

用卡诺图求最小项的操作:由最简式表示在卡诺图中,再写出卡诺图中该位的序数

第二章 组合逻辑

竞争冒险

可见,在组合逻辑电路中,当一个门电路输入两个向相反方向变化的互补信号时,则在输出端可能会产生尖峰干扰脉冲。

解决方法

-

加选通脉冲

-

修改逻辑设计

-

加滤波电容

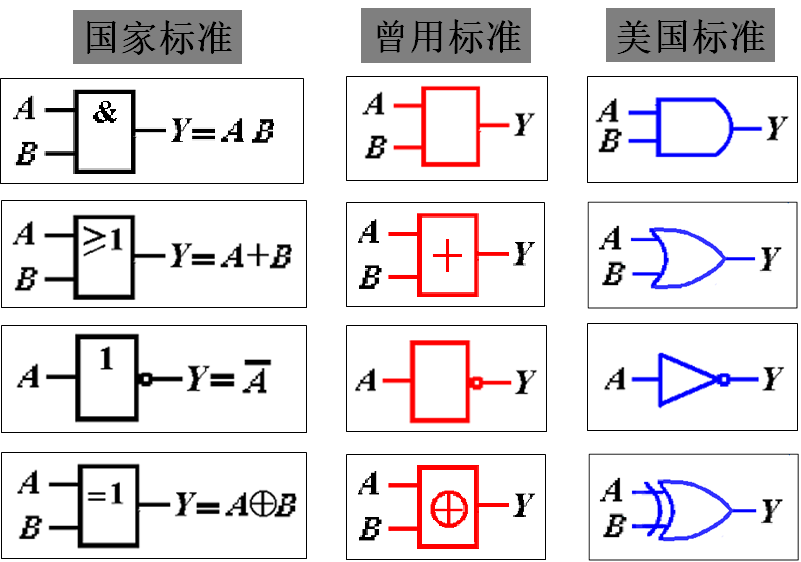

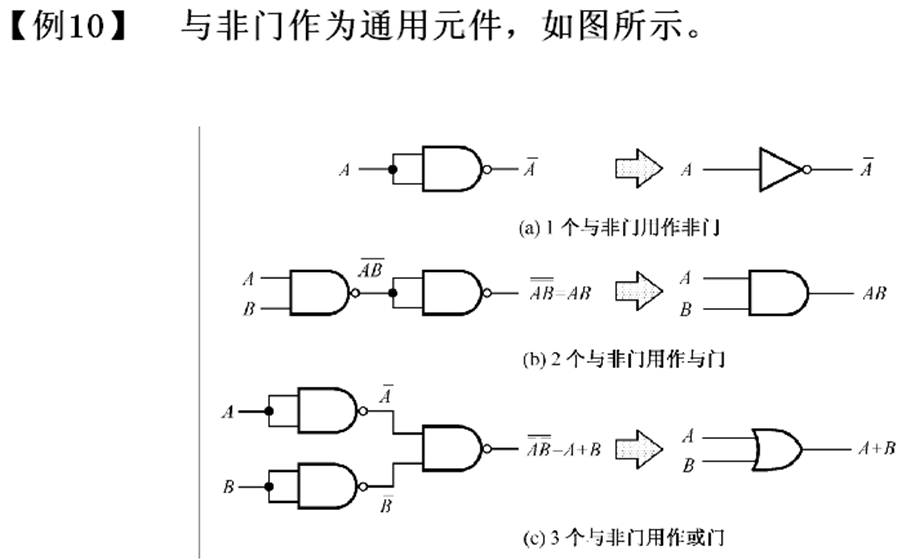

与非门搭积木

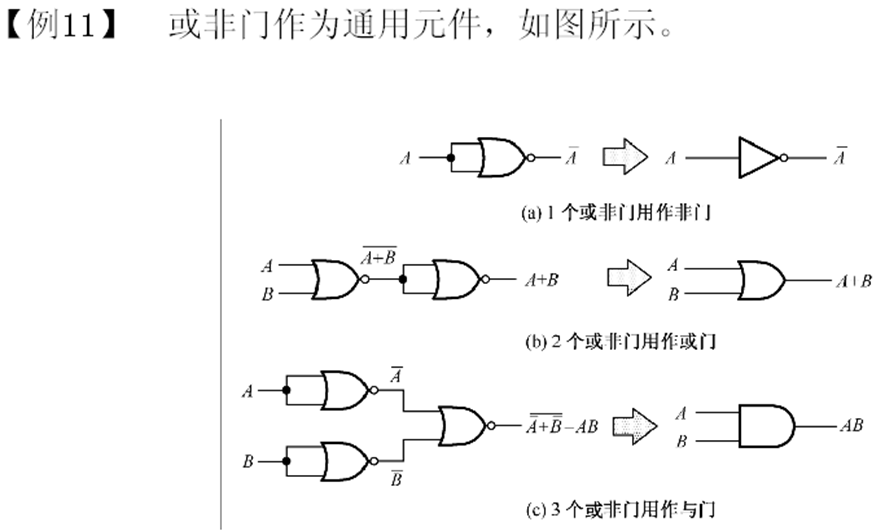

或非门搭积木

以下重点

数据选择器

多路输入,由控制信号决定输出哪一路的信号

四选一数据选择器74LS153

| 选择输入 | 数据输入 | 输出 | ||||

| A1 | A0 | D0 | D1 | D2 | D3 | Y |

| 0 | 0 | D0 | × | × | × | D0 |

| 0 | 1 | × | D1 | × | × | D1 |

| 1 | 0 | × | × | D2 | × | D2 |

| 1 | 1 | × | × | × | D3 | D3 |

还可以用两片74LS153组成双四选一选择器,功能同上,就是两片使用同一个A1,A0口

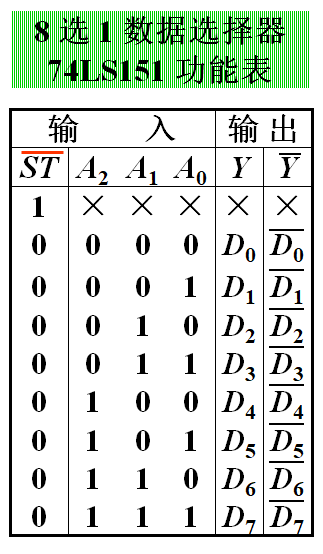

八选一数据选择器74LS151

- 注意使能端低电平有效,这是到现在为止第一个低电平有效的输入

- 观察得到,选择输入端,从高位起决定二进制数的高位,也就是”高位决定高位“

由代数法或者卡诺图法,用数据选择器表示逻辑式的步骤如下:

-

确定数据选择器的类型,一般有几个变量,就要选1的数据选择器

-

将输入逻辑式扩展至最小项表达式形式

-

将所选数据选择器的输出表达式与输入最小项表达式相对应 (使用代数法/卡诺图对照法)

-

写出表达式

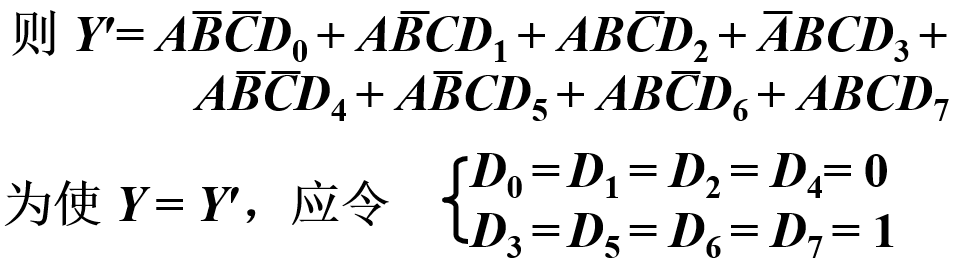

试用数据选择器实现函数 Y = AB + AC + BC

1.Y为三变量函数 ,故选用 8 选 1 数据选择器,现选用 74LS151

2.写出逻辑函数最小项表达式及数据选择器输出表达式

3.比较对应关系

A2=A,A1=B,A0=C,确定D0~Dn的值

卡诺图法操作同上:

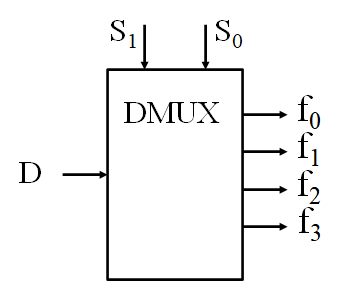

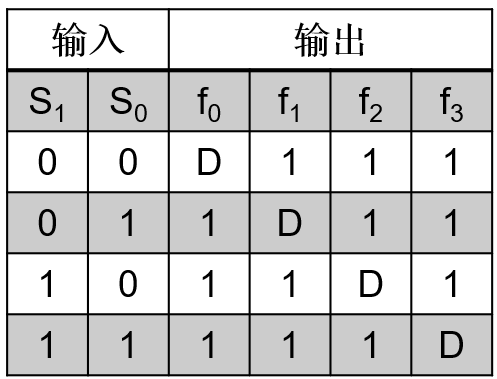

数据分配器

根据地址码的要求,将一路数据分配到指定输出通道上去的电路

可以通过把数据选择器和数据分配器连起来,Y连D,使两者的S口都输入同一个信号,这样可以通过输入不同的特定信号,实现Dn→fn的转换

我觉得没救了

第三章 时序逻辑电路

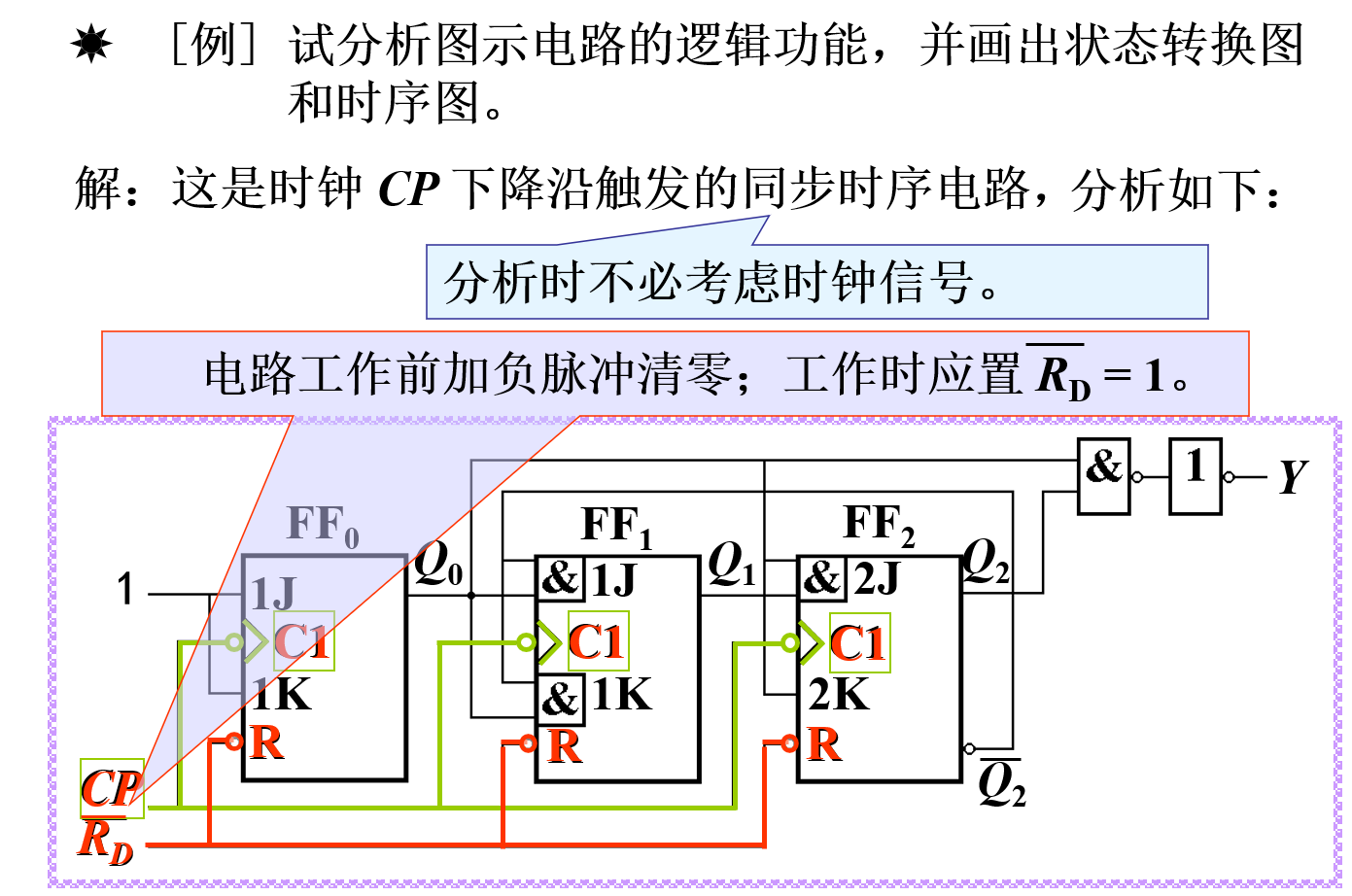

- 同步时序逻辑电路 所有触发器的时钟端连在一起。所有触发器在同一个时钟脉冲 CP 控制下同步工作

- 异步时序逻辑电路 时钟脉冲 CP 只触发部分触发器,其余触发器由电路内部信号触发。因此,触发器不在同一时钟作用下同步工作

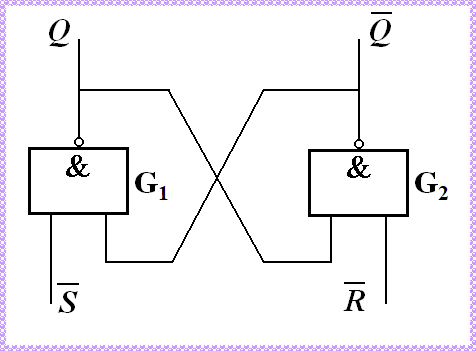

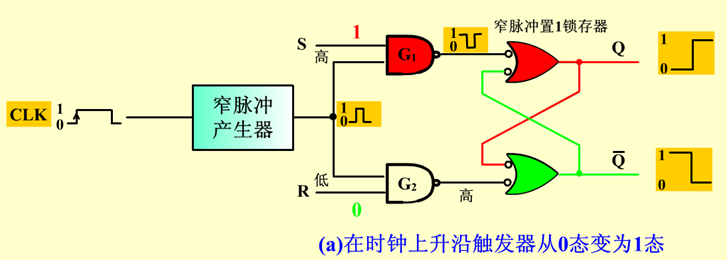

锁存器

- 有两个互补的输出和 。

- 有两个稳定状态(简称稳态),正好用来表示逻辑 0 和 1

- 在输入信号作用下,触发器的两个稳定状态可相互转换 (称为状态的翻转)。输入信号消失后,新状态可长期保持下来,因此具有记忆功能,可存储二进制信息

- 一般都用与非门

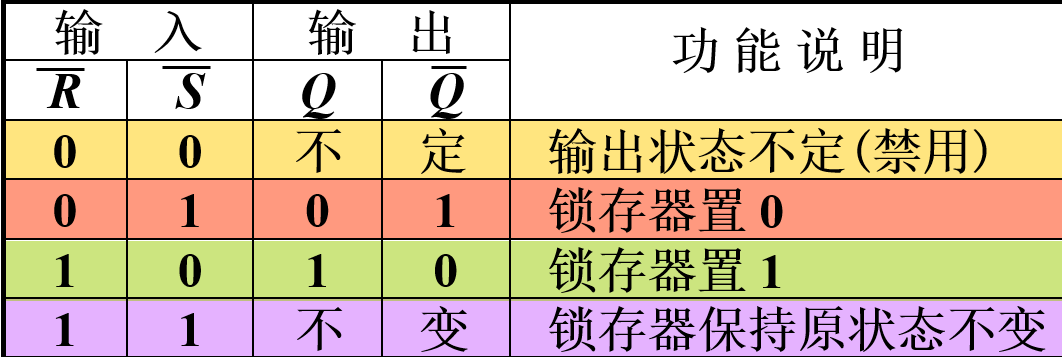

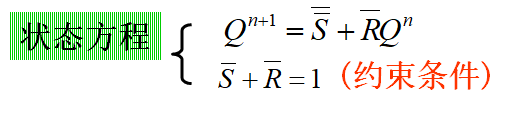

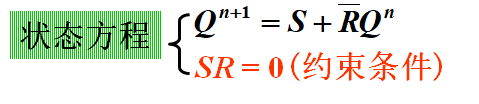

基本SR锁存器

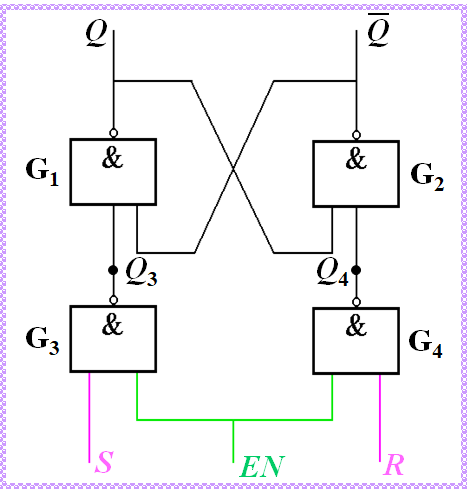

门控SR锁存器

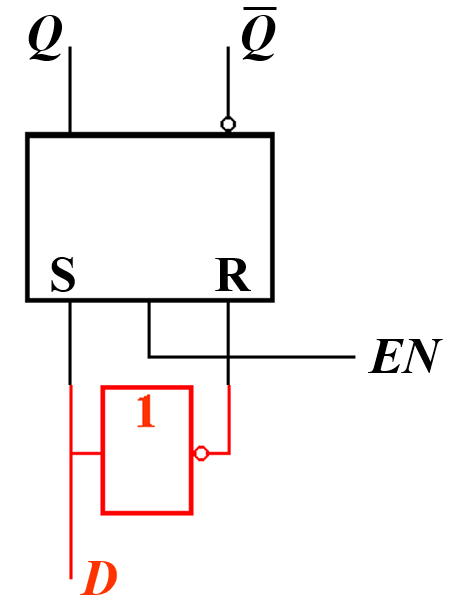

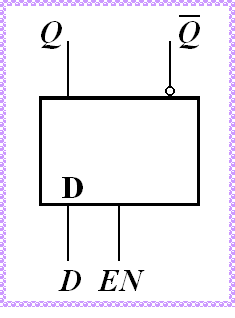

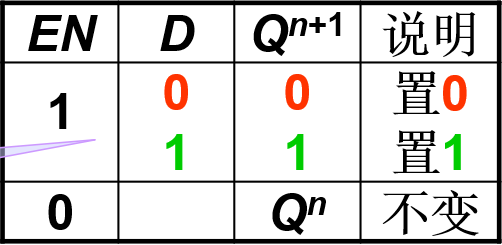

门控D锁存器

D锁存器在 EN = 1 期间能发生多次翻转,这种现象称为空翻

锁存器的触发方式为电平触发式,

锁存器的共同缺点是存在空翻

触发脉冲作用期间,输入信号发生多次变化时,锁存器输出状态也相应发生多次变化的现象称为空翻

触发器

- 有两个稳定状态(简称稳态),正好用来表示逻辑 0 和 1。

- 在输入信号作用下,触发器的两个稳定状态可相互转换(称为状态的翻转)。输入信号消失后,新状态可长期保持下来,因此具有记忆功能,可存储二进制信息。

特点:沿时钟边缘变化而变化

SR触发器

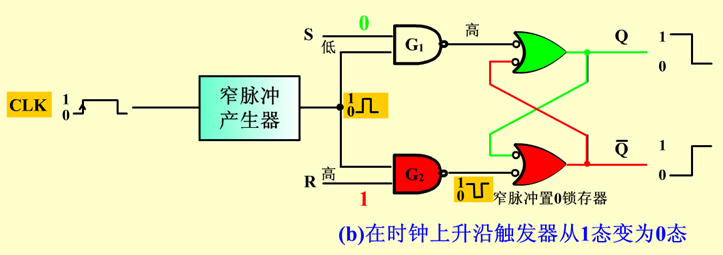

D触发器

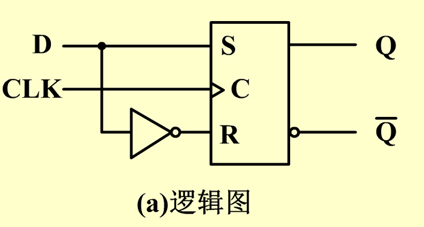

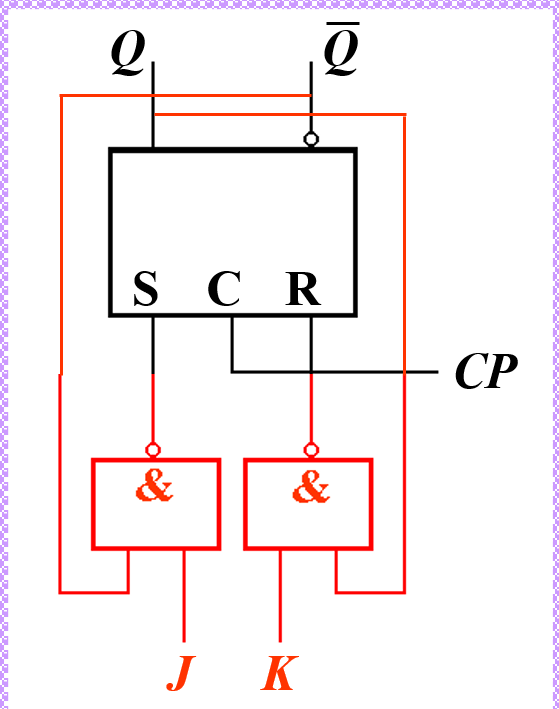

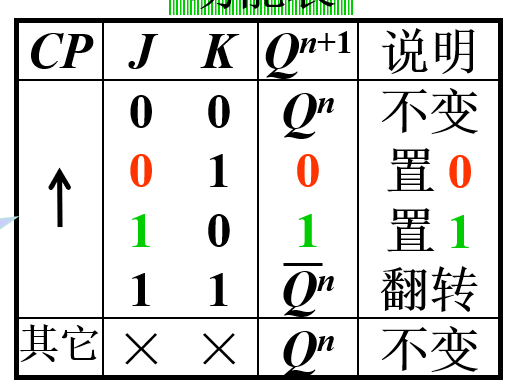

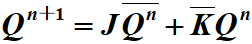

JK触发器

JK触发器存在两个强制端,低电平触发:

- PRE=0:触发器强制置1

- CLR=0:触发器强制置0

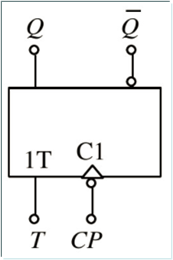

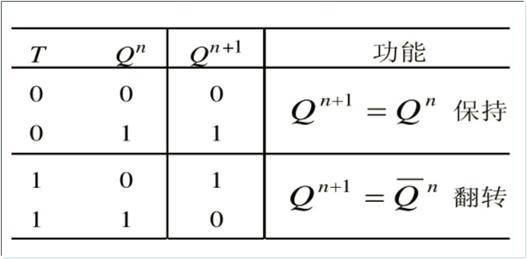

T触发器

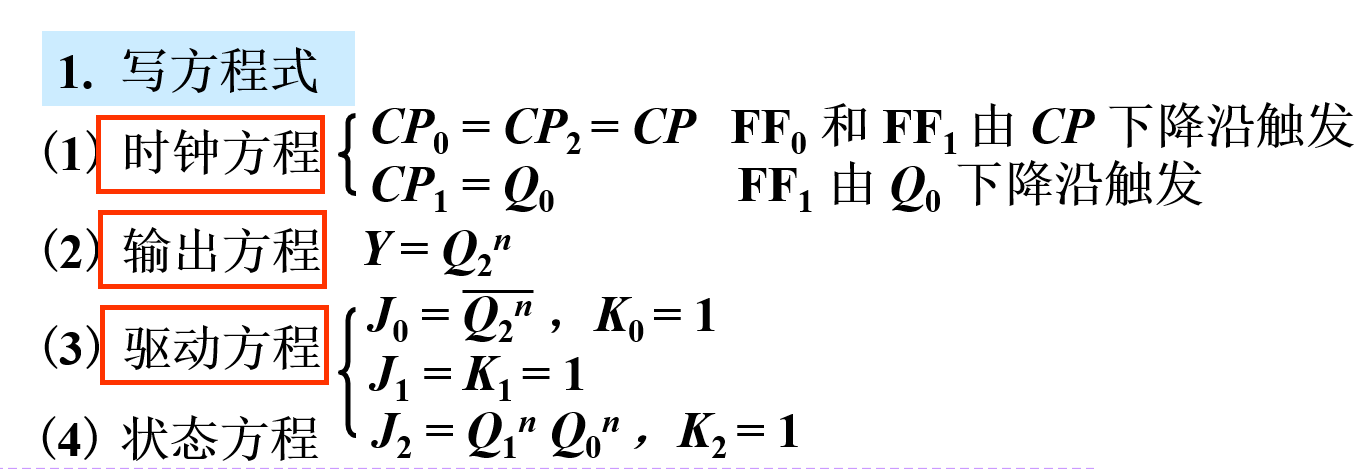

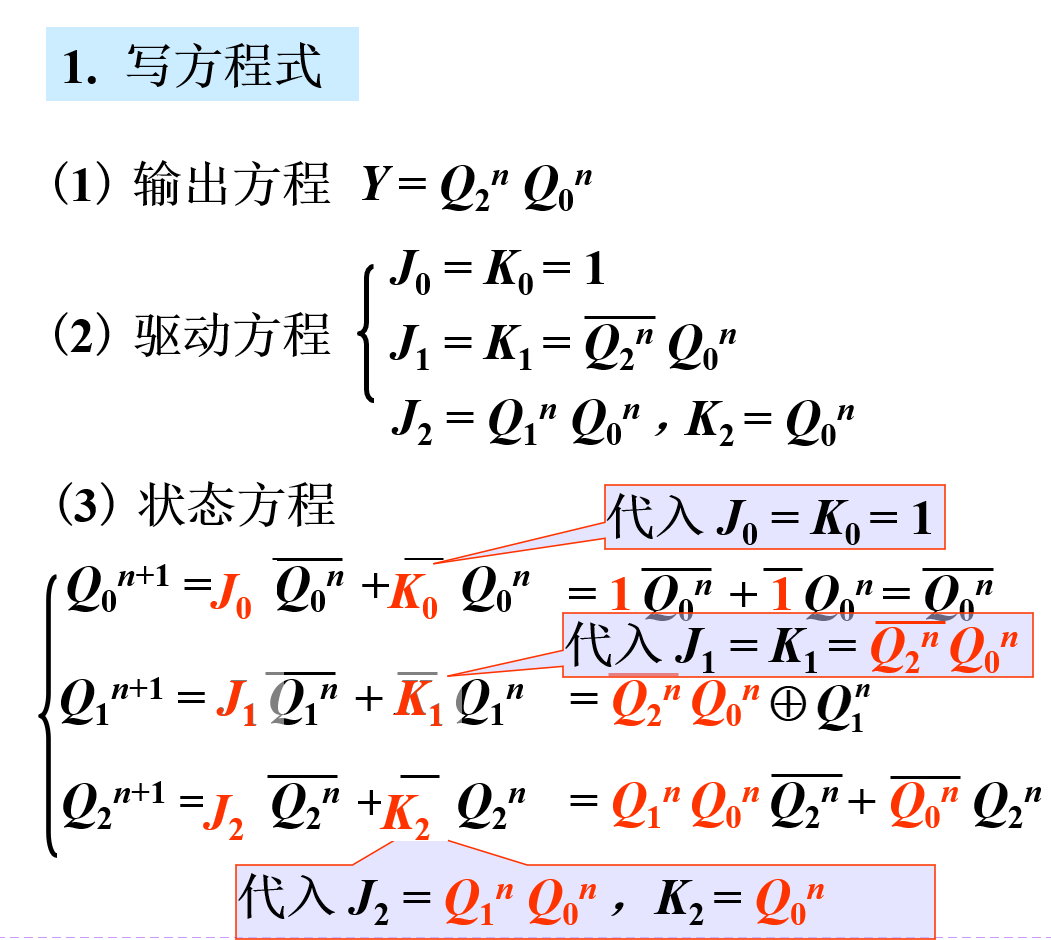

时序逻辑电路的分析方法

基本步骤:

- 根据给定的电路,写出它的输出方程和驱动方程(也称为激励方程、激励函数),并求状态方程

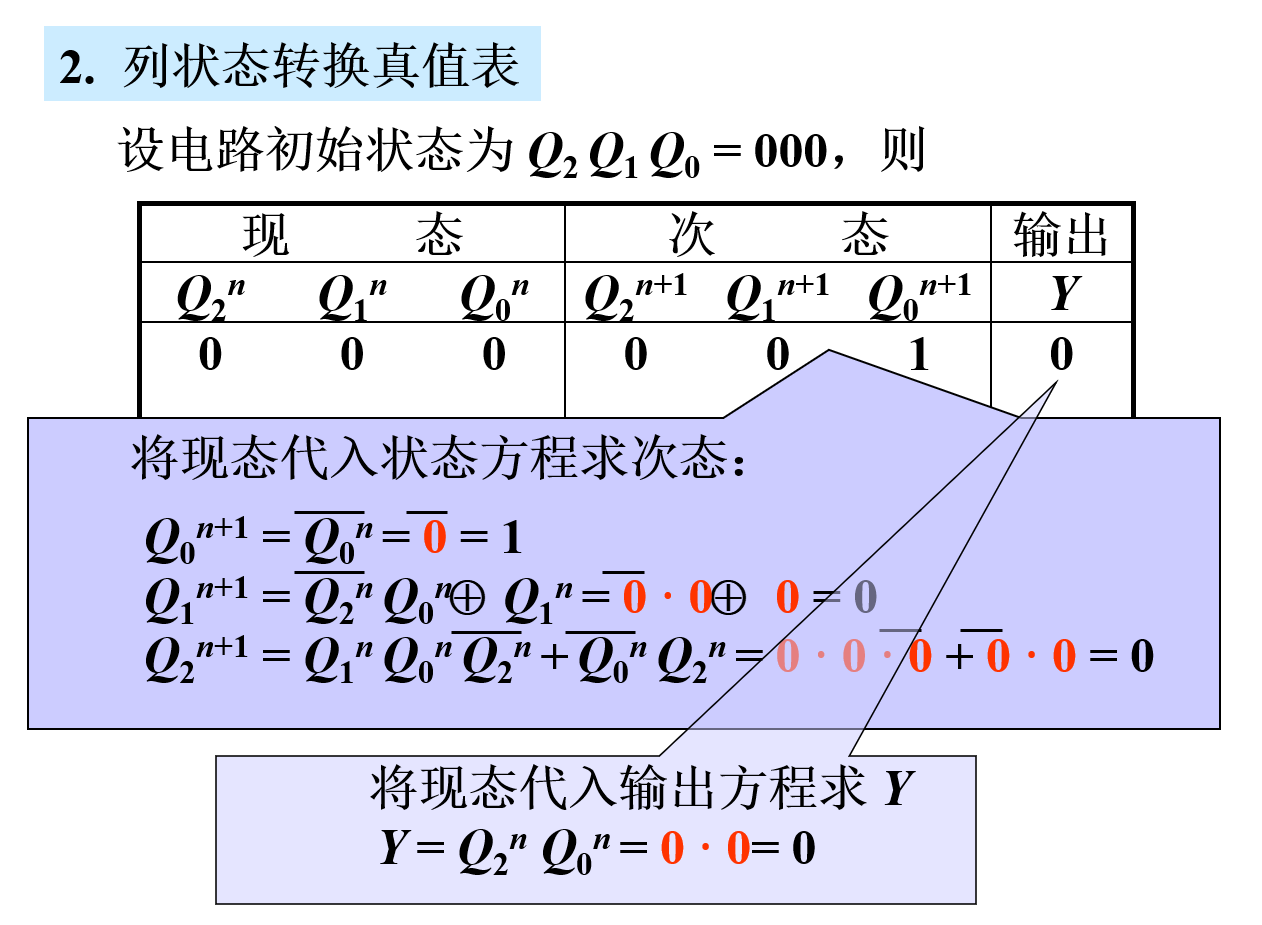

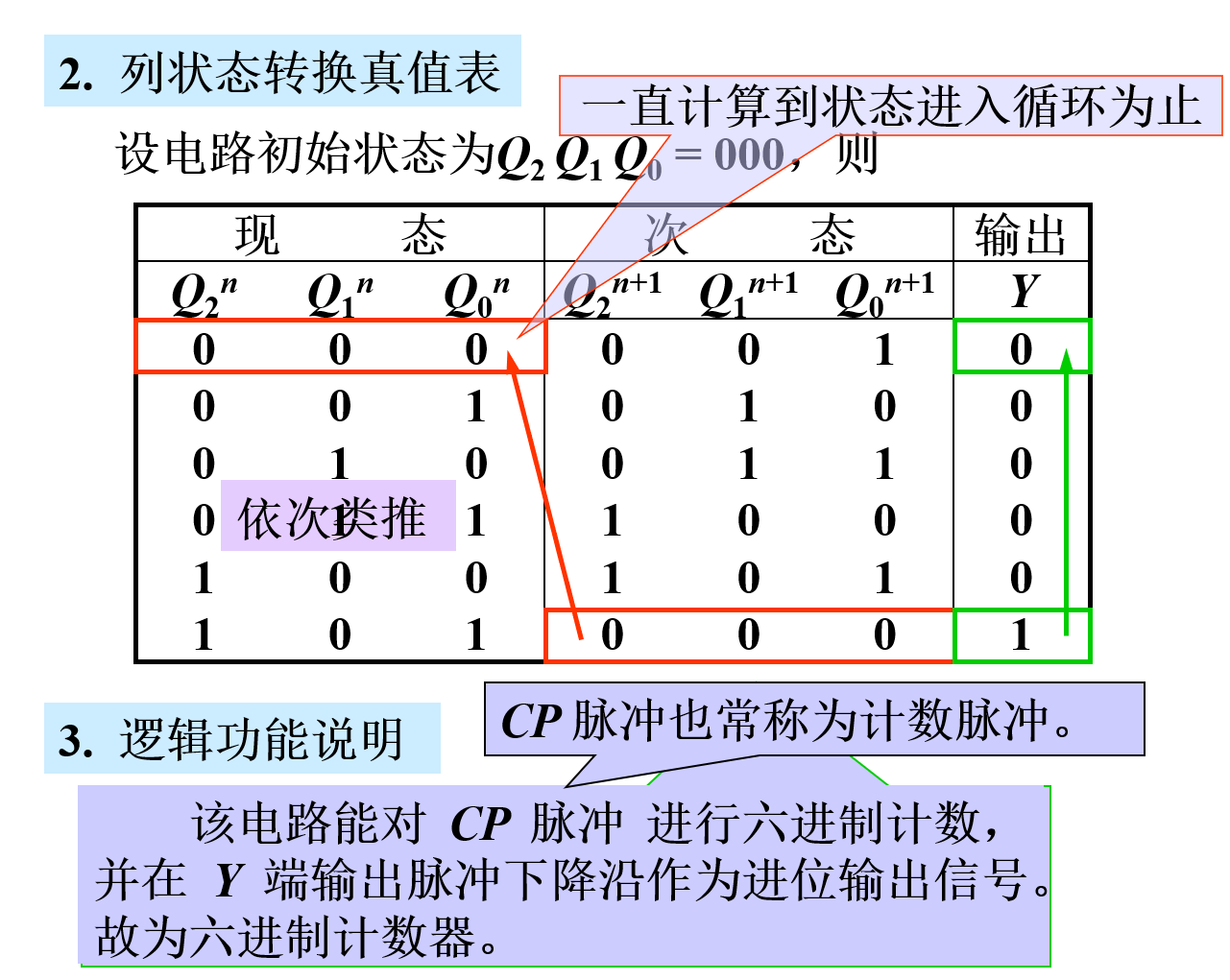

- 列状态转换真值表

- 画状态转换图和时序图

- 分析逻辑功能

同步逻辑

- 分析时不必考虑时钟信号

异步逻辑

- 分析异步时序电路时需写出时钟方程